In this article I upgraded my ECS Si5PI motherboard to a whopping 2MB of L2 cache. I was interested to see how much improvement the extra cache would bring. I remember reading advice in old Pentium-era magazines that further cache upgrades beyond 256kB offer only small returns. So let’s find out.

The testbed is as follows:

ECS Si5PI Socket 4 motherboard. PODP5V133 Pentium Overdrive CPU at 133 MHz. Diamond Stealth 64 DRAM VGA, 16 MB RAM. The system used SD-backed SCSI storage on Adaptec AHA-2940U SCSI controller. The OS was MS-DOS 6.0 + Windows 3.11.

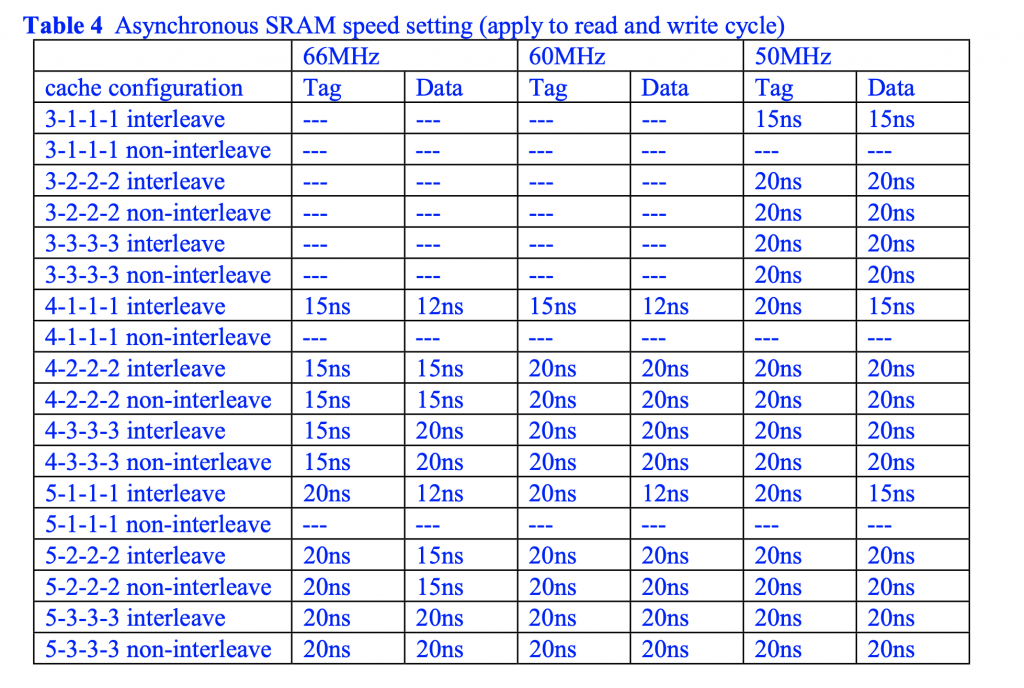

The task actually proved to be quite problematic. I found it difficult to maintain the same cache timings across all configurations. This is due to the fact that the L2 on this board can be configured as either single-bank (non-interleaved) or dual-bank (interleaved). Apart from higher capacity, the benefit of the latter is that it’s possible to use slower-ranked chips while maintaining the same access timings—or even using faster timings.

In the end, I used less aggressive timings (4-2-2-2 and 4-3-3-3), which allowed me to capture consistent results across all cache configurations.

Results

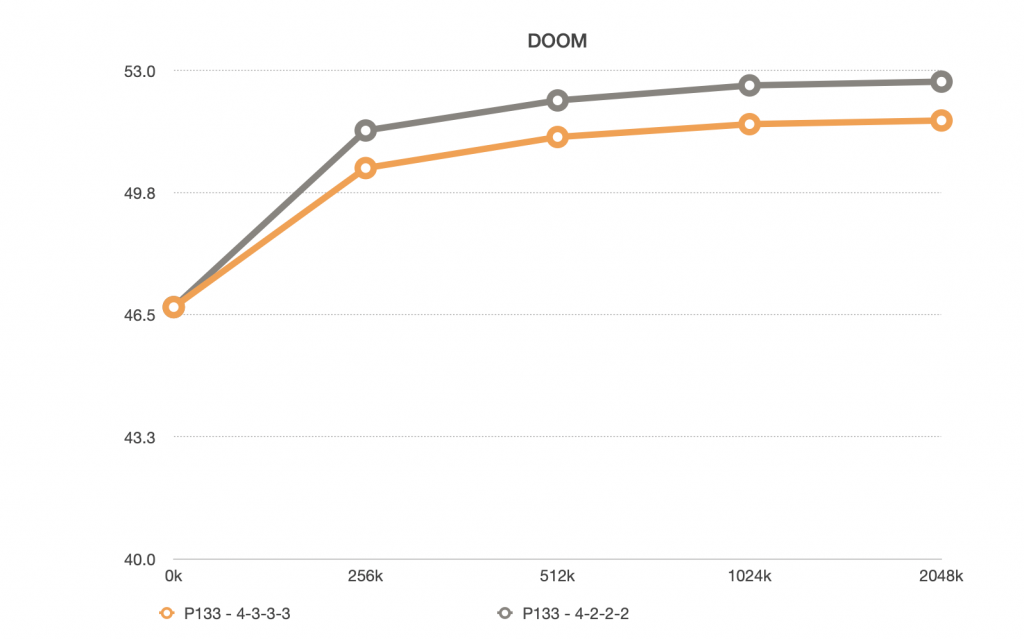

Doom

No surprise here. The Doom engine is no task for the CPU, and most cycles are wasted on VGA transfers. The test shows the typical “hockey stick” pattern, where the most benefit is realized simply by having any size of cache, and the improvement becomes negligible once you go past 1024K. In fact, even the difference between 512K and 1024K is tiny in absolute numbers—we’re talking about only a few real ticks less.

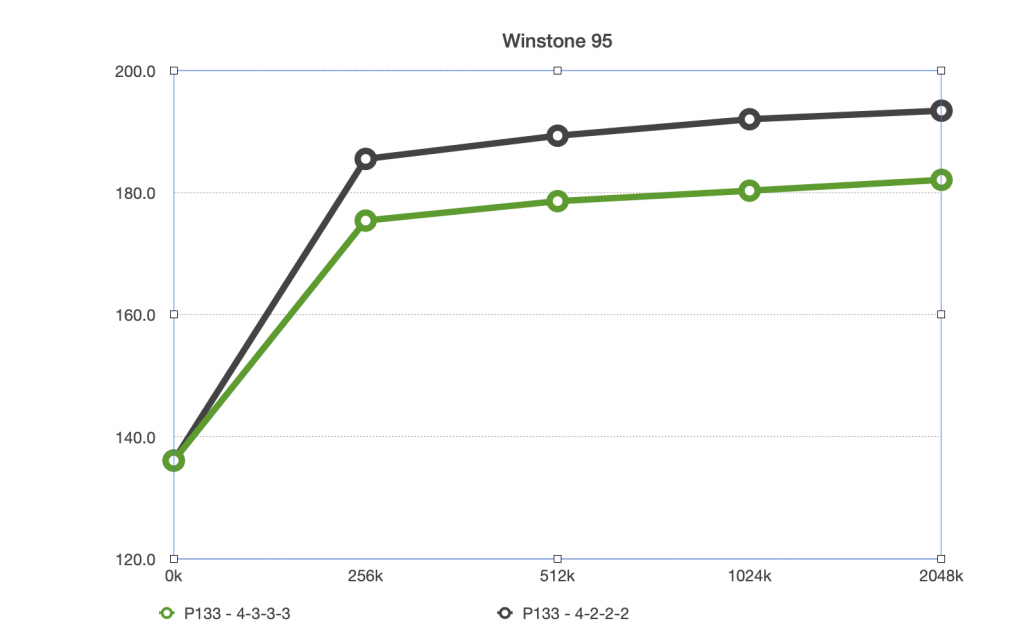

Winstone 95

Here you can see a similar story. Perhaps a bit more pronounced than in DOOM. Relatively slow gains past 256kB, but the performance still improves nevertheless. The cache timing is still way more important for the overall performance that the cache size.

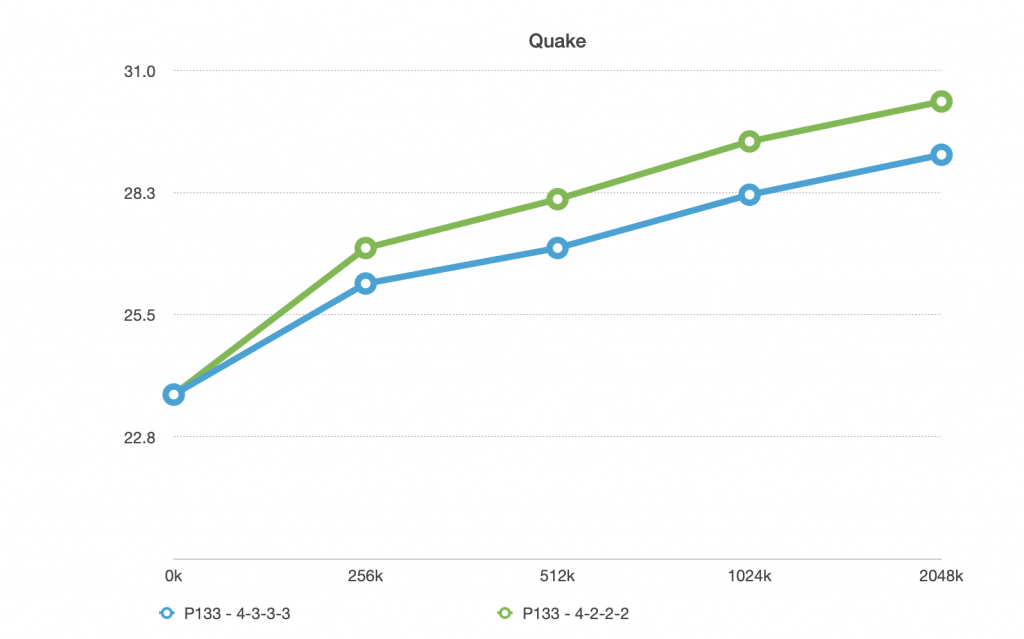

Quake 1.06

This might come as a surprise, but whatever Quake is doing with memory seems to improve nicely with an increase in L2 cache size. Even the step from 1024K to 2048K shows a healthy improvement. Cache timing is still important, but so is size.

Interesting to see that Quake is the only one that was able to take advantage of the a larger cache. I think one of the reasons everyone stuck to 256k was because that was the biggest bang for the buck. And consequently, I think developers just didn’t try to improve the code to work with anything beyond 256k. Chicken and egg as its best.

Very interesting – 2MiBs is beyond sweet. People would have creamed their pants about such a thing back in the day.(I usually go for 512KiB with these things.)

There were other manufacturers using the same chip-set – did you ever come across one of those?