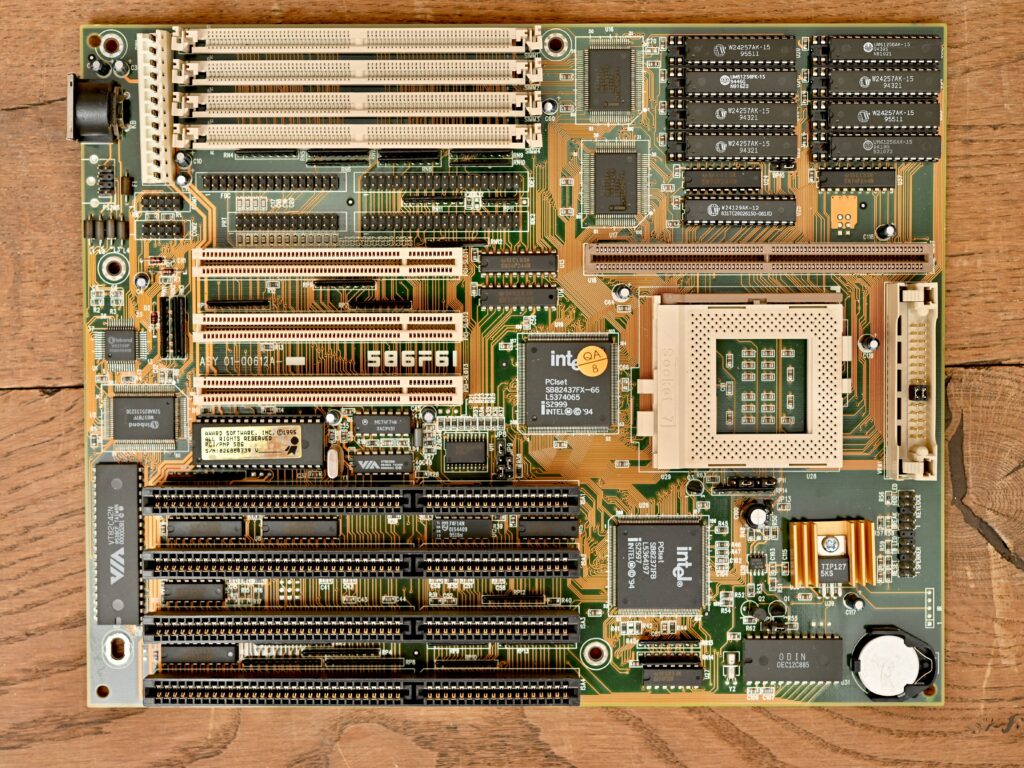

I’ve recently acquired an interesting motherboard with Intel 430FX Triton chipset.

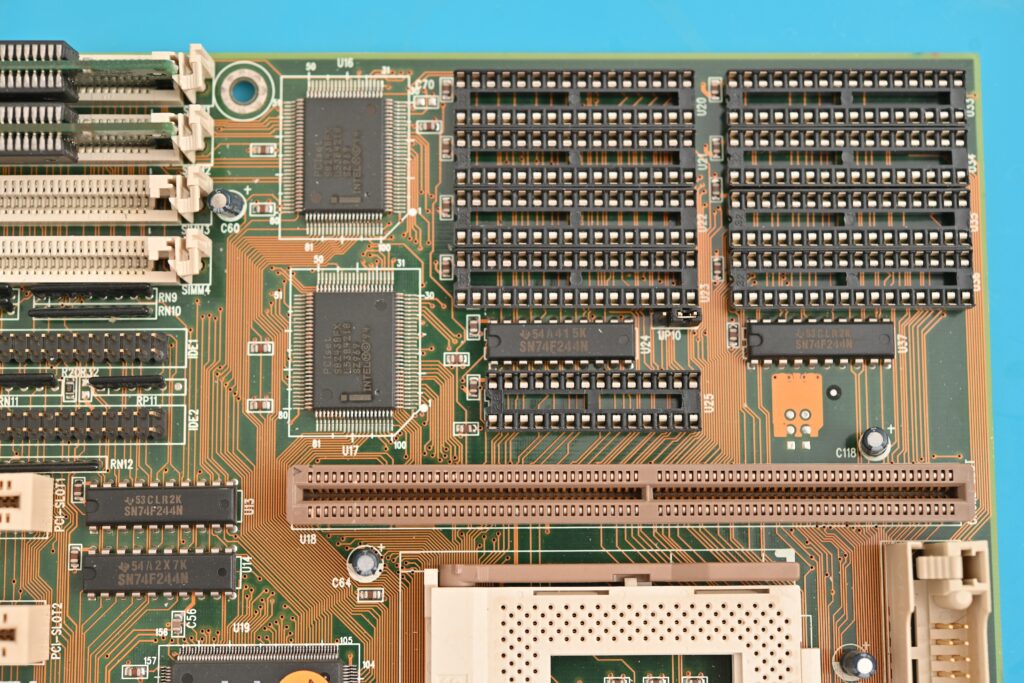

It has a feature I particularly wanted – sockets for asynchronous SRAM chips as well as a slot for COAST modules. Due to this, it allows for an interesting comparison of these two cache technologies.

Test environment:

- Freetech 485F61 motherboard in different cache configurations

- Intel Pentium 133 MHz CPU

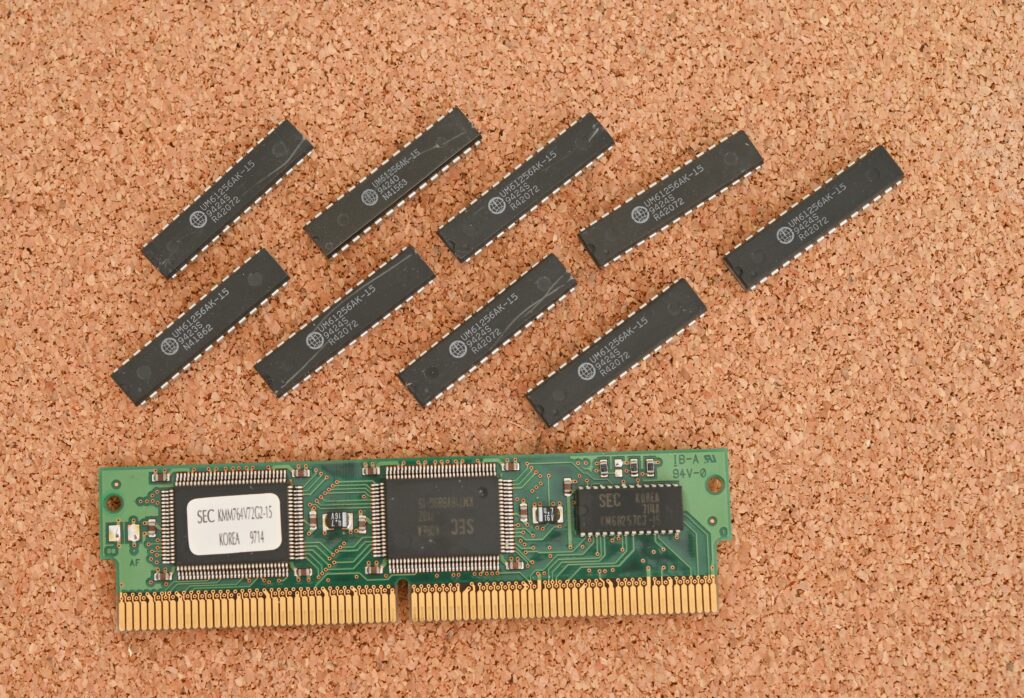

- 16 MB EDO RAM

- Diamond Stealth 64 Video 2001 PCI graphics card

- Adaptec AHA-2940U controller with SD2SCSI v6 storage

Results

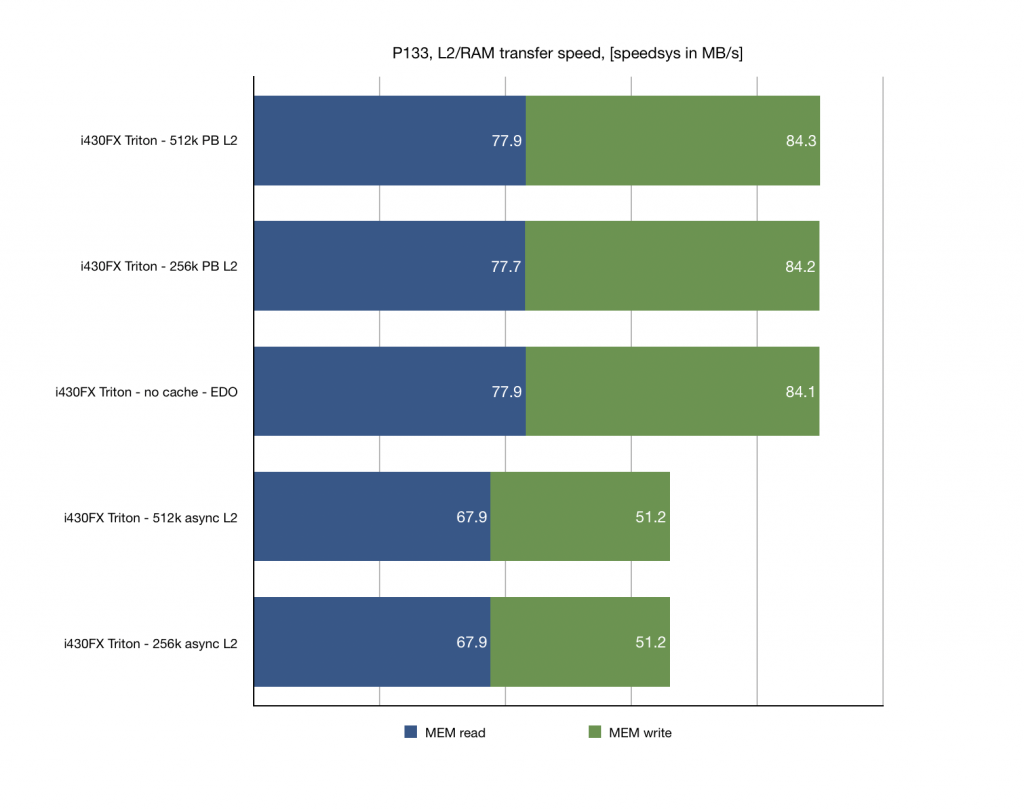

In its most common configuration with PB cache, the Intel Triton chipset provides a very solid class-leading RAM read/write performance. Especially with then-new EDO RAM modules. However, when asynchronous cache SRAMs are fitted the write performance goes down by more than 60%. This is even when compared with a system with no L2 cache:

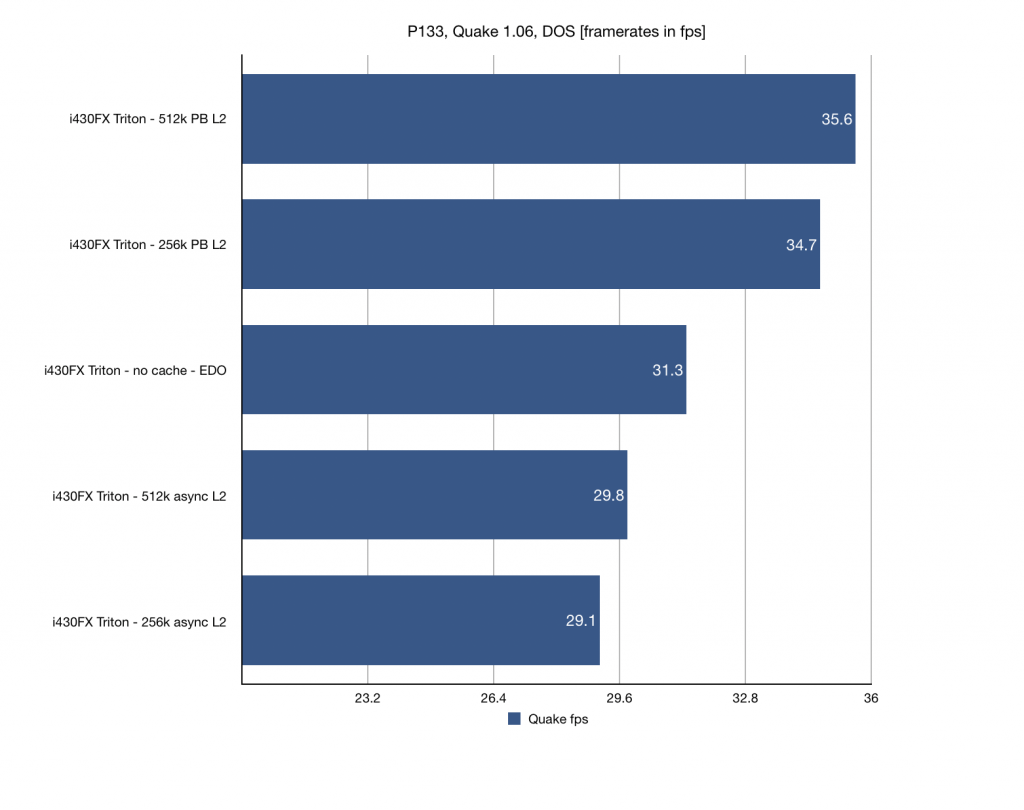

This obviously has a major impact on application performance. Such as the memory-intensive and write-heavy Quake benchmark:

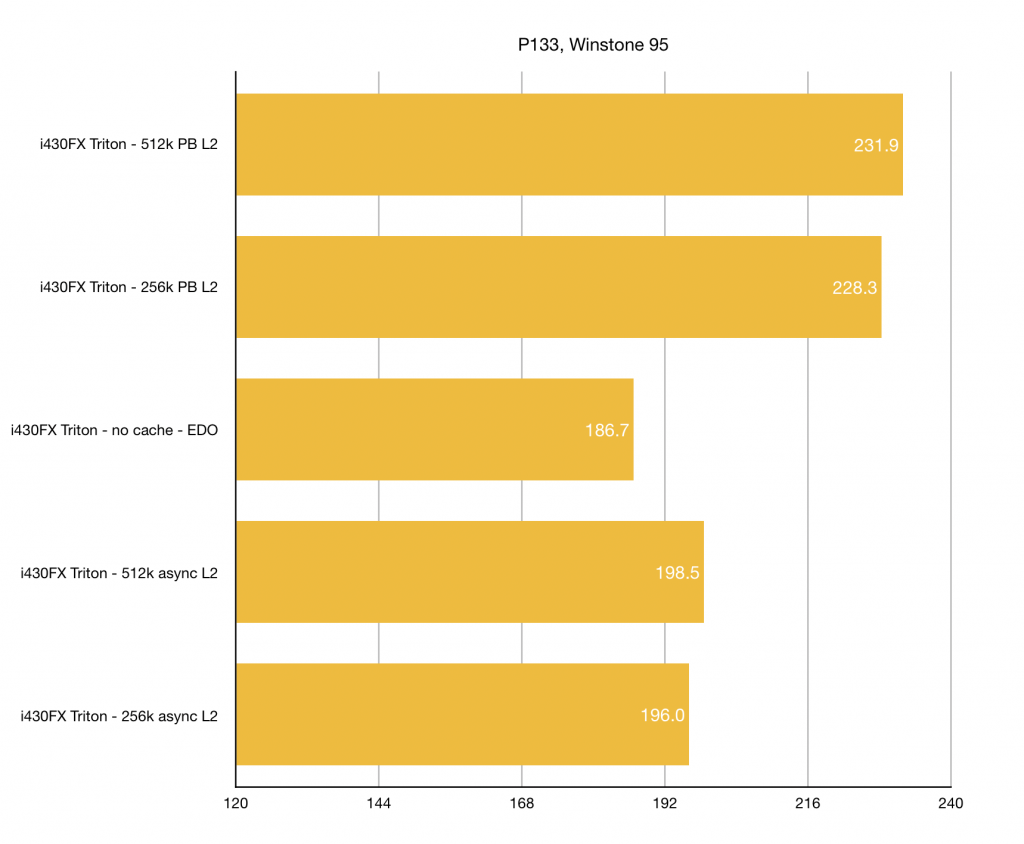

Yes. Removing SRAM chips from a motherboard improves performance in Quake by almost 8%! Fortunately, not every program is so write-heavy as Quake. Asynchronous SRAMs might be slow, but still getting data in 3-2-2-2 cycles from cache is faster than (7 to 12)-2-2-2 from EDO RAM or x-3-3-3 from FPM RAM which can win some performance back. That’s why benchmarks like Winstone 95 show a modest return when asynchronous cache:

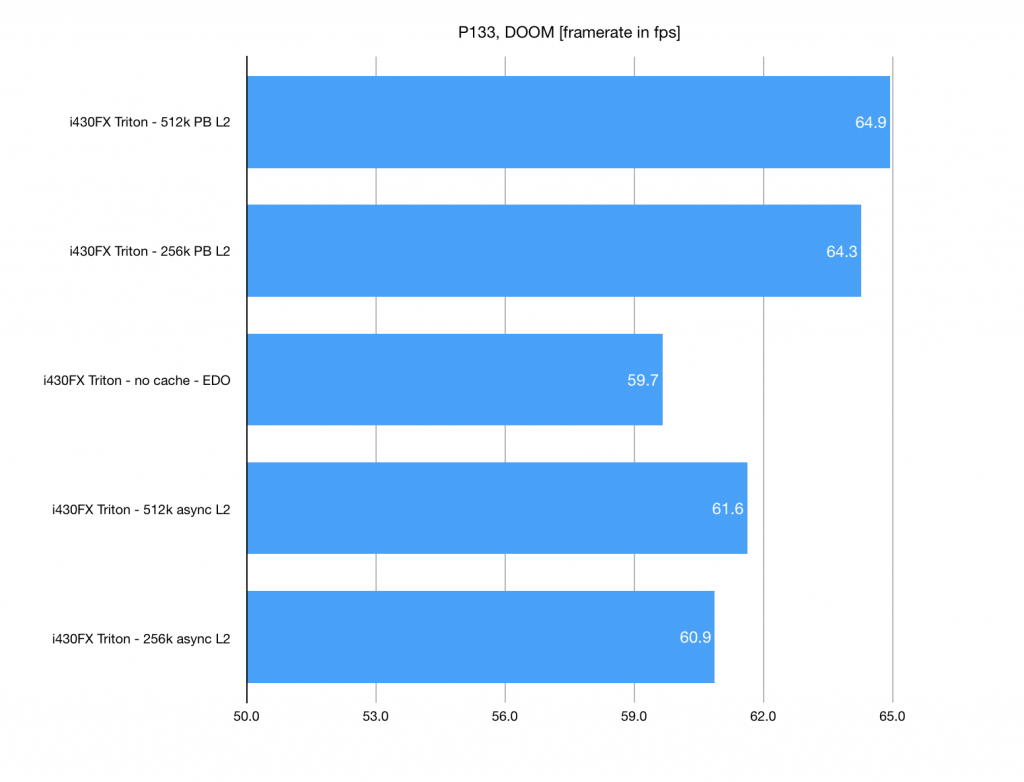

Similar situation in the DOOM:

Analysis

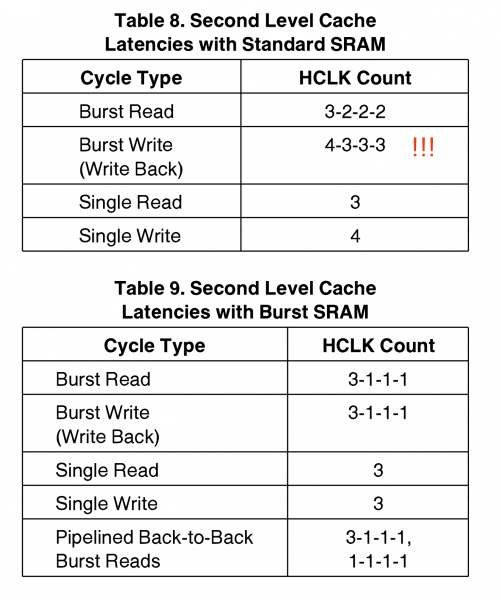

The Intel’s 430FX datasheet allows for an interesting explanation of the observed issue:

Burst writes with standard SRAMs are only performed at a pedestrian 4-3-3-3 latency. This is way slower than 3-1-1-1 of pipelined burst SRAMs and depending on circumstances (opened page, row set, etc.), it could be even slower than going directly to RAM. Unlike on other chipsets, this value is not programmable by chipset registers so this is not something where BIOS settings can help.

It is not clear what is the reason for such a big compromise. If some chipset bug or a deliberate design choice. What is clear is that other contemporary chipsets don’t exhibit this. Even Triton’s predecessors – 430LX/NX could do at least 4-2-2-2 writes and so do 3rd party chipsets from SiS or ALi. On the other hand, more modern Intel chipsets don’t support asynchronous SRAMs. So this remains a mystery.

As important as writes are, the async SRAMs still provide improvement for reads. Thus despite fighting an uphill battle the overall performance can still be improved by having an L2 cache.

The cache size difference 256k vs 512k is helping a bit. But all it can do is to improve the hit ratio. The cache timing is much more important performance factor that the cache size in most tests.

Conclusion

Although the i430FX chipset can be used with either SRAM types it is clear than only the pipelined burst is the only preferable choice. Still, in the early days, the Triton motherboards with asynchronous cache or cache-less were very common. Such as the popular Intel Zappa motherboards used by many OEM vendors. The explanation of this is simple. The advances of performance in Triton chipset are so high that with any cache configuration or even no cache at all, the Triton remains faster than predecessors or most 3rd party solutions. When compared with modern chipsets it is easy to miss that perspective. See my previous Early Pentium Chipsets article if you need proof.

I’m not very familiar with the Socket5 generation of boards, but I remember that at least some of them required 3.3V synchronous SRAM rather than 5V asynchronous.

I take it the only way to know for sure is to consult the user manual? Do you happen to have a PDF manual for your Freetech board?

Very interesting. I remember when the coast modules came out, but it was at a time of a lot of change so no one cared about off-die cache anymore.